|

|

Book

-

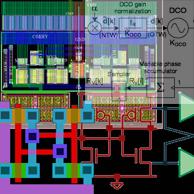

R. B. Staszewski and P. T. Balsara: All-Digital Frequency Synthesizer in Deep-Submicron CMOS,Wiley-Interscience, John Wiley & Sons, Hoboken, New Jersey, Sept. 2006. ISBN 0-471-77255-0.

Selected Publications

-

R. Venkatasubramanian, S. K. Manohar and P. T. Balsara: "NEM Relay Based Sequential Logic Circuits for Low Power Design," IEEE Transactions on Nanotechnology, vol. 12, no. 3, May 2013, pp. 386-398.

-

S. Modi, N. Yanduru, and P.T. Balsara:"Efficiency Improvement of Doherty Power Amplifier using Supply Switching and Gate Bias Modulationr," Proceeding of the 15th Annual IEEE Wireless and Microwave Technology Conference (WAMICON2014), Cocoa Beach, FL, April 13-15, 2014.

-

S. K. Manohar and P.T. Balsara:"94.6% Peak Efficiency DCM Buck Converter with Fast Adaptive Dead-Time Control," Proceeding of the 39th European Solid-State Circuits Conference (ESSCIRC), Bucharest, Romania, Sept 16-20, 2013, pp. 153-156.

-

E. Atalla, F. Zhang, A. Bellaouar, and P. T. Balsara:"Estimation of Passive Mixer Output Bandwidth Using Switched-Capacitor Techniques," Proceeding of the 2013 IEEE Custom Integrated Circuits Conference (CICC), Sept. 22-25, 2013.

-

I. Syllaios, and P. T. Balsara: "Linear Time-Variant Modeling and Analysis of All-Digital Phase-Locked Loops," IEEE Transactions on Circuits and Systems-I, vol. 59, No. 11, November 2012, pp. 2495-2506.

-

S. K. Manohar, R. Venkatasubramanian and P.T. Balsara:"Hybrid NEMS-CMOS DC-DC Converter for Improved Area and Power Efficiency," Proceedings of the 25th International Conference on VLSI Design (VLSI �12), Hyderabad, India, January 8-11, 2012, pp. 221-226.

-

R. Venkatasubramanian, S. K. Manohar and P. T. Balsara:"Ultra Low Power High Efficiency Charge Pump Design using NEM Relays," Proceedings of the IEEE Midwest Symposium on Circuits and Systems (MWCAS), 2011.

-

R. Venkatasubramanian, S. K. Manohar and P. T. Balsara:"Improving Performance of NEM Relay Logic Circuits using Integrated Charge-Boosting Flip-Flop," Proceedings of the IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH), 2011.

-

V.K.K. Srinivasan, C. K. Singh and P.T. Balsara: "A Generic Scalable Architecture for Min-Sum/Offset-Min-Sum Unit for Irregular/Regular LDPC Decoder,"IEEE Transactions on VLSI, vol. 18, No. 9, September 2010, pp. 11372-1376.

-

I. Syllaios, P. T. Balsara and R. B. Staszewski: "Recombination of Envelope and Phase Paths in Wideband Polar Transmitters,"IEEE Transactions on Circuits and Systems-I, vol. 57, No. 8, August 2010, pp. 1891-1904.

-

J. Mehta, V. Zoicas, O. E. Eliezer, R. B. Staszewski, S. Rezeq, M. Entezari and P.T. Balsara: "An Efficient Linearization Scheme for a Digital Polar Edge Transmitter,"IEEE Transactions on Circuits and Systems-II, vol. 57, No. 3, March 2010, pp. 193-197.

-

V. Parikh, P. T. Balsara and O. E. Eliezer: "All Digital Quadrature Modulator for Wideband Wireless Transmitters,"IEEE Transactions on Circuits and Systems-I, vol. 56, No. 11, November 2009, pp. 2487-2497.

-

O. Eliezer, B. Staszewski, S. Bhatara, I. Bashir & P. T. Balsara: "A Phase Domain Approach for Mitigation of Self-Interference in Wireless Transceivers,"IEEE Journal on Solid-State Circuits, vol. 44, No. 5, May 2009, pp. 1436-1453.

-

I. Elahi, K. Muhammad & P. T. Balsara: "Parallel Correction and Adaptation Engines for I/Q Mismatch Compensation,"IEEE Transactions on Circuits and System-II, vol. 56, No. 1, January 2009, pp. 86-90.

-

S. Modi, S. Kanigere, O. Eliezer and P. T. Balsara: Limited Bandwidth Envelope Follower for Improving Efficiency of Broadband Linear Power Amplifier," Proceeding of the 7th IEEE Dallas Circuits and Systems Workshop (DCAS '08), Richardson, Texas. Oct. 19-20, 2008, pp. 66-69.

-

I. Syllaios, P. T. Balsara and R. B. Staszewski: "Time-Domain Modeling of a Phase-Domain All-Digital PLL," IEEE Transactions on Circuits and Systems-II, vol. 5, No. 6, June 2008, pp. 601-605.

-

V. Parikh, P.T. Balsara and O. Eliezer: "A Low Area and Low Power Digital Band-Pass Sigma-Delta Modulator for Wireless Transmitters," Proceedings of the IEEE International Conference on Circuits and Systems (ISCAS), 2007, pp. 3279-3282.

-

R. Staszewski and P. T. Balsara: "All-Digital PLL with Ultra Fast Settling," IEEE Transactions on Circuits and Systems-II, vol. 54, No. 2, Feb. 2007, pp. 181-185

-

C. Singh, S. Honnavara Prasad and P.T. Balsara: "VLSI Architecture for Matrix Inversion using Modified Gram-Schmidt based QR Decomposition," Proceedings of the 20th IEEE International Conference on VLSI Design (VLSI '07), Bangalore, India. Jan. 6-10, 2007, pp. 836-841.

-

I. Elahi, K. Muhammad & P. T. Balsara: "IIP2 and DC Offsets in the Presence of Leakage at LO Frequency," IEEE Transactions on Circuits and Systems-II, vol. 53, No. 8, Aug. 2006, pp. 647-651

-

I. L. Syllaios, P. T. Balsara & O. Eliezer: "A Generalized Signal Reconstruction Method for Designing Interpolation Filters," Proceedings of the IEEE International Conference on Circuits and Systems (ISCAS), Kos, Greece, May 2006, pp. 5768-5771.

-

M. J. Akhbarizadeh, M. Nourani, Deepak-Sarathi V., & P. T. Balsara: "A Non-Redundant Ternary CAM Circuit for Network Search-Engines," IEEE Transactions on VLSI Systems, vol. 14, No. 3, March 2006, pp. 268-278.

-

R. Staszewski, S. Vemulapalli, P. Vallur, J. Wallberg & P. T. Balsara: "1.3V 20ps Time-to-Digital Converter in 90nm CMOS," IEEE Transactions on Circuits and Systems-II, vol. 53, No. 3, March 2006, pp. 220-224.

-

I. Elahi, K. Muhammad & P. T. Balsara: "I/Q Mismatch Compensation Using Adaptive Decorrelation in a Low-IF Receiver in 90nm CMOS Process," IEEE Journal on Solid-State Circuits, vol. 41, No. 2, February 2006, pp. 395-404.

-

V. Ramakrishnan and P.T. Balsara: "A Wide-Range High-Resolution Compact CMOS Time to Digital Converter," Proceedings of the 19th IEEE International Conference on VLSI Design (VLSI '06), Hyderabad, India, January 3-7, 2006, pp. 197-202.

-

R. Staszewski, Chan Fernando & P. T. Balsara: "Event-Driven Simulation and Modeling of an RF Oscillator," IEEE Transactions on Circuits and Systems-I, Vol. 52, No. 4, April 2005, pp. 723-732.

-

R. Staszewski, & P. T. Balsara: "Phase-Domain All-Digital Phase-Locked Loop," IEEE Transactions on Circuits and Systems-II, Vol. 52, No. 3, March 2005, pp. 159-163

-

I. Elahi, K. Muhammad & P. T. Balsara: "I/Q Mismatch Compensation in a low-IF Receiver in 90nm CMOS Process," Proceeding of the IEEE International Solid-State Circuits Conference, San Francisco, CA, February 6-10, 2005.

-

R. Vilangudipitchai & P. T. Balsara: "Power Switch Network Design for MTCMOS," 18th International Conference on VLSI Design (VLSI '05), Kolkata, India, January 2005. pp. 6C:1-4.

-

R. Bharadwaj, R. Konar, P. T. Balsara & D. Bhatia: "Exploiting Temporal Idleness to Reduce Leakage Power in Programmable Architectures," Asia and South Pacific Design Automation Conference (ASP-DAC), Shanghai, China, Jan. 18-21, 2005. pp. 651-656.

-

R. B. Staszewski, K. Muhammad, D. Leipold, C-M Hung, Y-C Ho, J. Wallberg, C. Fernando, K. Maggio, R. Staszewski, J. Koh, S. John, I. Deng, V. Sarda, O. Moreira, V. Mayega, R. Katz, O. Friedman, O. Eliezer & P. T. Balsara: "All-Digital TX Frequency Synthesizer and Discrete-Time Receiver for Bluetooth Radio in 130 nm CMOS Process," IEEE Journal of Solid-State Circuits, Vol. 39, No. 12, Dec. 2004, pp. 2278-2291

-

R. Staszewski, D. Leipold, & P. T. Balsara: "Just-In-Time Gain Estimation of an RF Digitally-Controlled Oscillator for Digital Direct Frequency Modulation," IEEE Transactions on Circuits and Systems-II, Vol. 50, No. 11, Nov. 2003, pp. 887-892

-

R. Staszewski, C-M Hung, D. Liepold & P. T. Balsara: "A First Multi-GHz Digitally Controlled Oscillator For Wireless Applications," IEEE Transactions on Microwave Theory and Techniques, Vol. 51, No. 11, Nov. 2003, pp. 2154-2164.

-

L. Holla, P. Vallur, P. T. Balsara, A. Navada & S. Shastry: "A Fast 16-bit TSPC Adder in SOI CMOS," Proceedings of the 7th IEEE VLSI Design and Test Workshop, Bangalore, India, Aug. 28-30, 2003, pp. 55-60.

-

K. Muhammad, R. Staszewski, & P. T. Balsara: "Challenges in Integrated CMOS Transceivers for Short Distance Wireless", Great Lakes VLSI Symposium, 2001 (Invited), pp. 45-50.

-

R. Staszewski, K. Muhammad & P. T. Balsara: "A Constrained Asymmetry LMS Algorithm for PRML Disk Drive Read Channels", IEEE Transactions on Circuits and Systems-II: Analog and Digital Signal Processing, Vol. 48, No. 8, August 2001, pp. 793-798.

-

K. Muhammad, R. Staszewski & P. T. Balsara: "Speed, Power, Area and Latency Tradeoffs in Adaptive FIR Filtering for PRML Read Channels", IEEE Transactions on VLSI Systems, Vol. 9, No. 1, February 2001, pp. 42-51.

-

R. Staszewski, K. Muhammad & P. T. Balsara: "A 550 Msps 8-Tap FIR Digital Filter for Magnetic Recording Read Channel," IEEE Journal of Solid-State Circuits, Vol. 35, No. 8, August 2000, pp. 1205-121.

|

|